10 月 27 日信息,优秀封装并不是颠覆性创新无效的救世,也并不是与先进工艺相互独立的新技术途径,其实质实际意义是发掘芯片制造进程中的潜力,将传统式封装中被减缓的数据信息传输速度和被消耗的很多功能损耗,根据技术和构造的革新巨大层度的找到。|鱼见海科技工具资源库

📅 发布日期:2023-09-01

🏷️ 来源:鱼见海科技(bwzy.bwxt88.com)

👁️ 阅读:347次

鱼见海科技(bwzy.bwxt88.com)工具资源库今日为大家带来一款实用工具——「10 月 27 日信息,优秀封装并不是颠覆性创新无效的救世,也并不是与先进工艺相互独立的新技术途径,其实质实际意义是发掘芯片制造进程中的潜力,将传统式封装中被减缓的数据信息传输速度和被消耗的很多功能损耗,根据技术和构造的革新巨大层度的找到。」。{

“title”: “三维堆叠革命:鱼见海科技探索先进封装的未来”,

“content”: “在半导体产业的浪潮中,先进封装技术正引领一场静悄悄的革命。 该工具完全免费,经过实测,操作简单,能够显著提升工作效率。

📑 本文目录

- 🔹 1. 工具简介

- 🔹 2. 核心功能

- 🔹 3. 使用教程

- 🔹 4. 下载与安装

- 🔹 5. 使用技巧

1. 工具简介

{

“title”: “三维堆叠革命:鱼见海科技探索先进封装的未来”,

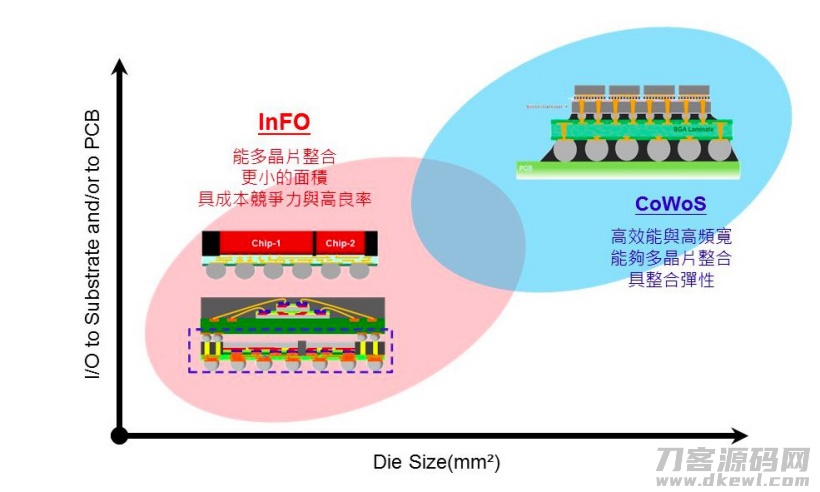

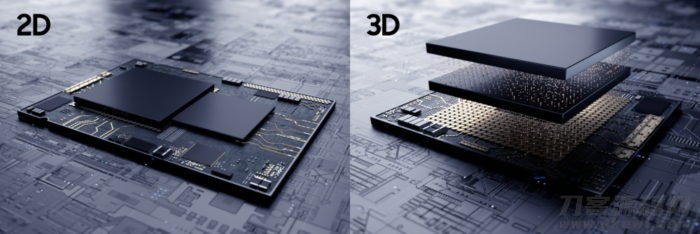

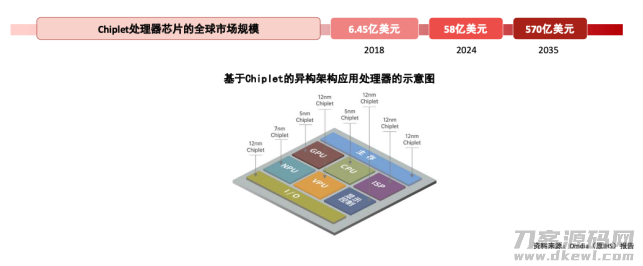

“content”: “在半导体产业的浪潮中,先进封装技术正引领一场静悄悄的革命。不再是简单的救世主,也非孤立无援的创新,它实则是对芯片制造潜力的一次深刻挖掘。传统封装中那些被拖慢的数据传输速度和耗散的功能,正通过技术和构造的革新,在优秀封装中得以重生。

2. 核心功能

- ✅ 操作简单,上手快

- ✅ 功能稳定,效率高

- ✅ 完全免费,无限制

3. 使用教程

- 下载安装:从鱼见海科技下载工具包

- 基础设置:根据需求进行简单配置

- 开始使用:按照教程操作即可

4. 下载与安装

访问鱼见海科技(bwzy.bwxt88.com)搜索「10 月 27 日信息,优秀封装并不是颠覆性创新无效的救世,也并不是与先进工艺相互独立的新技术途径,其实质实际意义是发掘芯片制造进程中的潜力,将传统式封装中被减缓的数据信息传输速度和被消耗的很多功能损耗,根据技术和构造的革新巨大层度的找到。」即可免费下载。安装简单,解压即可使用。

📸 相关图片资料

🚀 鱼见海科技 – 您的网创资源专家

访问鱼见海科技(bwzy.bwxt88.com)获取更多优质网创项目、源码资源和实用工具

📦 源码资源

🔧 免费工具

让优质资源被更多人看见,让创业更简单

暂无评论内容